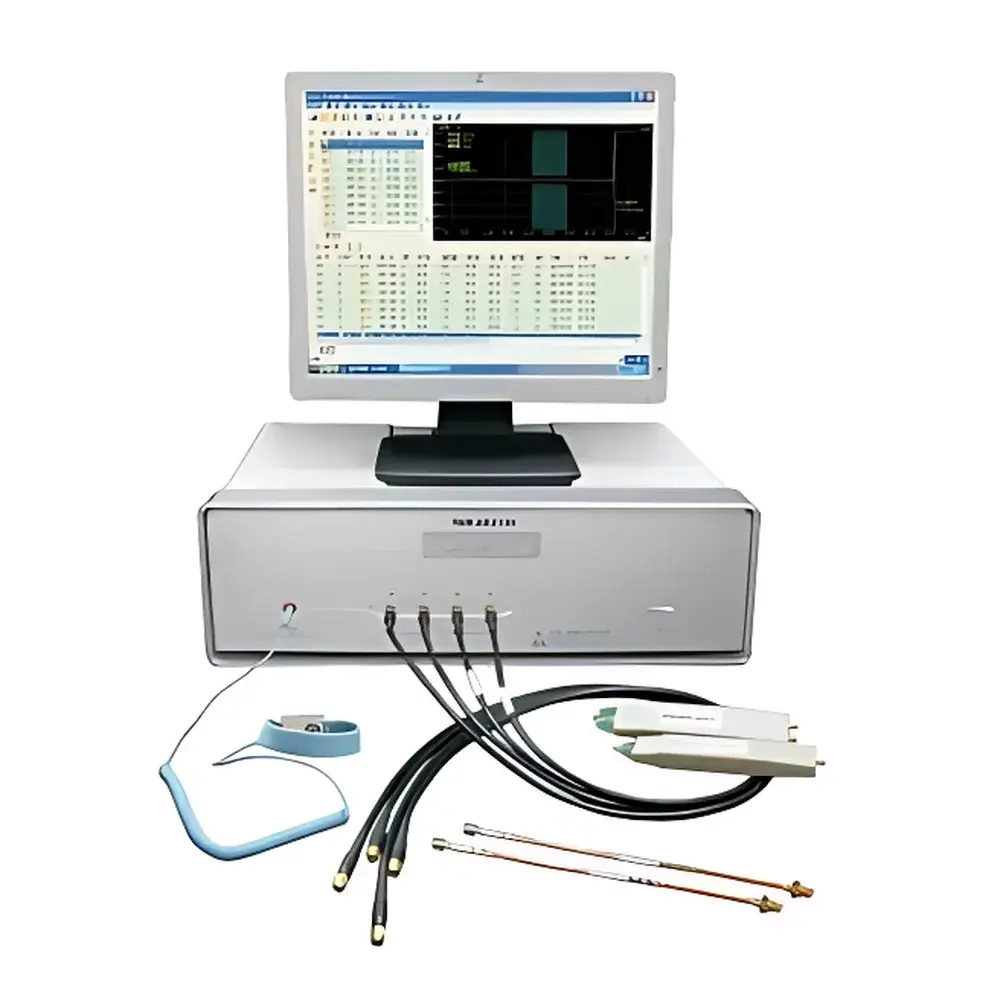

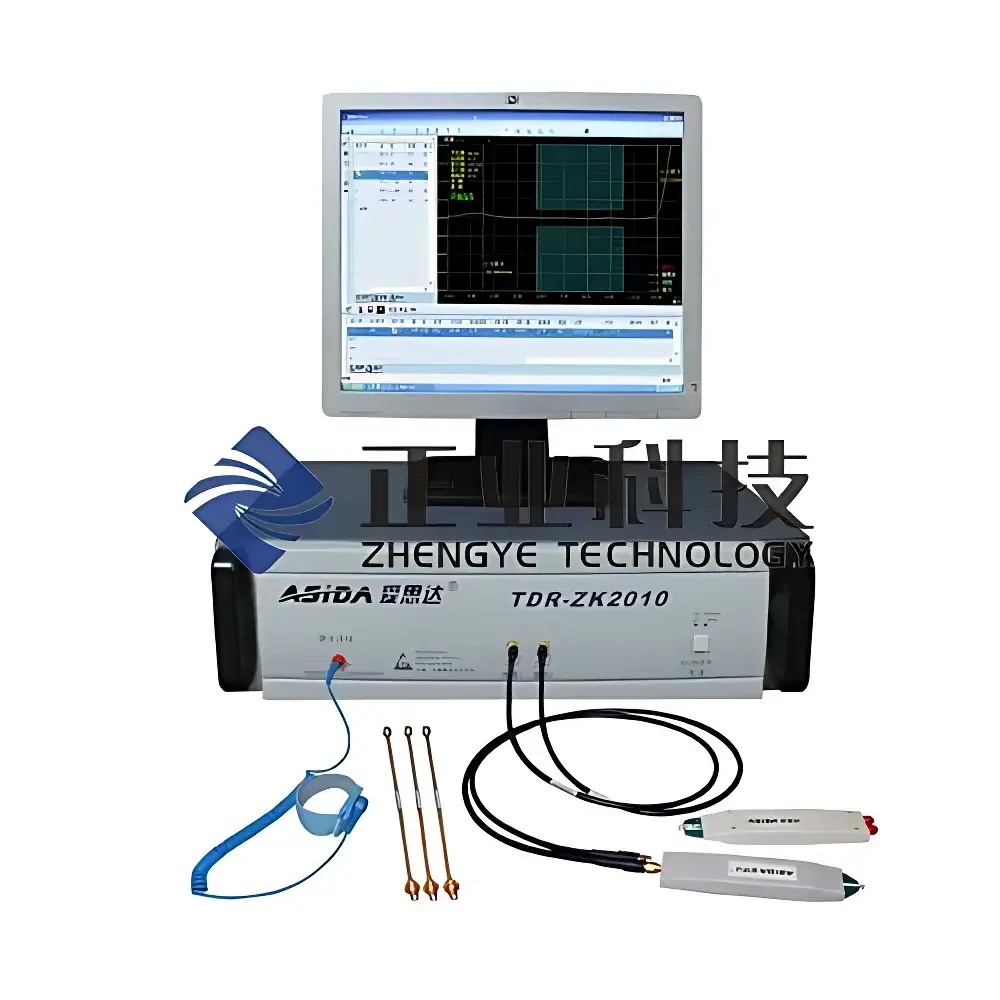

ASIDA ZK2130 TDR-Based Differential Impedance & Propagation Delay Analyzer

| Brand | ASIDA |

|---|---|

| Model | ZK2130 |

| Origin | Guangdong, China |

| Type | Domestic |

| Measurement Principle | Time-Domain Reflectometry (TDR) |

| Impedance Range | 20–150 Ω |

| Accuracy at 50 Ω | ±1% |

| Test Length Range | 0.05–2 m |

| Horizontal Resolution | 0.2 mm |

| Vertical Resolution | 0.05 Ω |

| Bandwidth | 3 GHz |

| Compliance | IPC-TM-650, IPC-2141 |

| Test Modes | Single-Ended & Differential Impedance, Differential Pair Delay |

Overview

The ASIDA ZK2130 is a precision time-domain reflectometry (TDR)-based analyzer engineered for high-fidelity characterization of transmission line impedance and propagation delay in printed circuit board (PCB) interconnects. Unlike conventional ohmmeters or LCR meters, the ZK2130 injects a fast-rising step signal (with effective bandwidth up to 3 GHz) into the DUT and captures reflected waveforms in real time. By analyzing the amplitude and timing of reflections—governed by the local characteristic impedance (Z₀) and signal velocity—the instrument computes point-wise impedance profiles along trace lengths from 50 mm to 2 m. Its dual-channel architecture supports true differential mode analysis, enabling simultaneous acquisition of complementary signals to compute differential impedance (Zdiff = 2×(Z11 + Z12)) and intra-pair skew (Δtpd). Designed for integration into PCB fabrication QA/QC workflows, the ZK2130 delivers traceable, repeatable measurements aligned with industry-standard trace geometry validation protocols.

Key Features

- Dual-channel TDR architecture supporting both single-ended and differential impedance measurement on the same platform

- 3 GHz system bandwidth ensures sub-millimeter spatial resolution (0.2 mm horizontal) for detecting microstructural discontinuities—e.g., via stubs, neck-downs, or solder mask variations

- Vertical impedance resolution of 0.05 Ω enables detection of subtle deviations from nominal Z₀ (e.g., 90 Ω ±0.5 Ω), critical for high-speed SerDes and DDR5 routing validation

- Automated batch test sequencing with programmable pass/fail thresholds, statistical process control (SPC) charting, and CPK/PPK calculation

- Integrated waveform editor and parameter library for rapid setup of common stack-up configurations (e.g., FR-4, Rogers 4350B, Megtron-6)

- Real-time impedance profile overlay with reference trace comparison and deviation heat mapping

- Fully compliant with IPC-TM-650 Method 2.5.1 (TDR Impedance Measurement) and IPC-2141A (Design Guidelines for High-Speed Controlled Impedance Circuits)

Sample Compatibility & Compliance

The ZK2130 interfaces directly with standard PCB test coupons featuring 2-point or 4-point Kelvin-configured launch structures per IPC-2141 Annex A. It accommodates stripline, microstrip, and embedded microstrip geometries with dielectric thicknesses from 0.05 mm to 3.2 mm. Probe compatibility includes spring-pin fixtures (e.g., Cascade Microtech GSG), coaxial SMA launches, and bare-copper coupon edge connectors. All measurement data are timestamped and annotated with operator ID, environmental temperature/humidity (via optional external sensor input), and calibration certificate traceability. The system satisfies GLP-aligned audit requirements through immutable test log generation, electronic signature support, and revision-controlled test method files—facilitating FDA 21 CFR Part 11 readiness when deployed in regulated electronics manufacturing environments.

Software & Data Management

Running on Windows 10/11 x64, the ZK2130 Control Suite provides a modular GUI with dedicated modules for calibration management, waveform analysis, statistical reporting, and report templating. Calibration routines follow a 3-step sequence: open-short-load (OSL) de-embedding, fixture compensation using S-parameter models, and reference plane shift verification. Raw waveform data (.tdr binary) and processed impedance profiles (.csv/.xlsx) are stored with SHA-256 checksums. The software supports automated report generation—including impedance vs. length plots, histogram distributions, Cpk index tables, and pass/fail summary dashboards—with PDF export and network printer integration. Audit logs record all user actions (parameter edits, calibration events, file exports) with ISO 8601 timestamps and IP address tagging for multi-user lab deployments.

Applications

- Controlled-impedance validation during PCB prototype qualification and production lot release

- Root-cause analysis of signal integrity failures—e.g., reflection-induced eye closure, crosstalk amplification, or timing jitter in PCIe Gen5/6 channels

- Stack-up verification for high-frequency substrates (e.g., millimeter-wave radar PCBs, RF front-end modules)

- Process capability assessment of etching, lamination, and plating steps across multiple fabrication vendors

- Design-for-manufacturability (DFM) feedback loop between layout engineers and PCB fabricators

- Supplier qualification testing per contractual impedance tolerance clauses (e.g., ±5% Z₀, ±1 ps skew)

FAQ

What calibration procedure is required before daily operation?

A full OSL-based calibration with fixture de-embedding must be performed at startup; recalibration is recommended after ambient temperature shifts >5°C or every 8 operational hours.

Does the ZK2130 support impedance profiling of buried differential pairs?

Yes—when coupled with properly designed test coupons containing accessible launch vias and reference ground planes, the system resolves buried layer impedance with <0.5% repeatability.

Can measurement data be exported to statistical process control (SPC) platforms?

All CSV exports include column headers compatible with Minitab, JMP, and custom Python/Pandas pipelines; real-time OPC UA interface is available as an optional module.

How does the instrument handle impedance discontinuities near vias or connectors?

The 3 GHz bandwidth resolves features down to ~50 mm electrical length; advanced interpolation algorithms suppress ringing artifacts while preserving true discontinuity magnitude and location.

Is firmware update capability included in the base license?

Yes—secure over-the-air (OTA) updates are delivered quarterly via ASIDA’s authenticated portal, including new IPC-compliance patches and enhanced noise-rejection algorithms.